CMOS器件ESD防护网络设计技术探讨

CMOS 器件 ESD 防护网络的核心是快速泄放 + 精准钳位 + 多级协同 + 版图优化,在不影响正常功能的前提下,将 ESD 脉冲能量从 I/O/Power 端口安全泄放至地 / 电源,保护栅氧、漏结与互连线。下面从设计目标、主流结构、分级架构、版图与验证、高速 / 高压场景、趋势挑战六个维度展开技术探讨。

一、设计核心目标与失效机理

1. 核心目标

- 泄放:为 ESD 电流提供低阻抗、高可靠的旁路,绕过敏感核心电路。

- 钳位:将受保护节点电压钳制在器件安全工作窗口内(如 1.8V I/O:钳位 <4V;栅氧击穿电压> 6V)。

- 兼容:不影响正常工作(漏电流、寄生电容、速度),满足 JEDEC HBM/MM/CDM 标准。

- 鲁棒:耐受 HBM≥2kV、CDM≥500V,无闩锁(Latch-up)、无二次击穿。

2. CMOS ESD 失效机理

- 栅氧击穿:ESD 高压(kV 级)直接击穿薄栅氧(nm 级),不可逆失效。

- 漏结热烧毁:ESD 大电流(A 级)导致局部过热,金属 / 硅熔融。

- 互连线熔断:ESD 脉冲峰值电流超过金属线宽承载能力。

- 闩锁效应(Latch-up):寄生 PNPN 导通,电源 - 地短路,芯片烧毁。

二、主流 ESD 防护器件结构(芯片级)

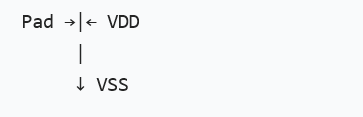

1. 二极管(Diode)—— 基础防护

- 结构:N+/P-well(正向)、P+/N-well(反向)、背靠背双向二极管。

- 原理:正向导通(Vf≈0.7V)泄放电流;反向雪崩击穿(Vbr≈VDD+0.7V)钳位高压。

- 特点:结构简单、速度快、寄生电容小;通流能力弱,适合低压、小电流场景。

- 应用:I/O 端口基础防护、电源轨钳位、二级精细钳位。

2. GGNMOS/GGPMOS(栅接地 MOS)—— 主流选择

- 结构:NMOS 栅极接地(GGNMOS)、PMOS 栅极接 VDD(GGPMOS),漏极接 Pad,源极接地 / VDD。

- 原理:ESD 脉冲使漏端雪崩,产生空穴电流抬高衬底电位,触发寄生 NPN/PNP导通,泄放大电流。

-

设计要点:

- 多 Finger 并联提升通流,Finger 宽度匹配工艺规则。

- 源端加Ballast 电阻(多晶硅 / 扩散电阻)抑制电流集中、防止热点。

- 采用Silicide Block工艺提高 Ballast 均匀性。

- 特点:CMOS 工艺兼容、通流能力强、成本低;钳位电压较高(≈10–15V),需配合二级防护。

- 应用:I/O 主保护、电源钳位。

3. SCR(Silicon Controlled Rectifier,晶闸管)—— 高压大电流

- 结构:PNPN 四层结构,触发后维持低阻导通。

- 原理:ESD 脉冲触发 NPN/PNP 正反馈,进入Latch-up 态,泄放极大电流。

-

优化结构:

- LVTSCR:低触发电压(≈3–5V),兼容 1.8V/2.5V I/O。

- Diode-Triggered SCR:二极管辅助触发,响应速度 ns 级。

- 特点:通流能力最强、钳位电压低(≈1–2V)、面积效率最高;触发电压不易控、易闩锁、设计复杂。

- 应用:高压 I/O、电源端口、高等级 ESD 需求(HBM≥8kV)。

4. RC-CLAMP(电源轨钳位)—— 全局防护

- 结构:RC 延迟网络 + GGNMOS/SCR,跨接 VDD–VSS。

- 原理:ESD 脉冲时,电容快速充电、电阻延迟,使 MOS 栅极抬升导通,泄放电源轨 ESD 电流。

- 设计要点:RC 时间常数匹配 ESD 脉冲宽度(≈100ns),避免正常工作误触发。

- 特点:覆盖全芯片电源域、抑制地弹;寄生电容大,影响电源噪声。

- 应用:芯片级电源 ESD 防护、多电源域协同。

5. 其他结构

- 厚氧器件(FOD):高压工艺专用,耐受更高 ESD 电压。

- TVS(片上 / 片外):片上集成 TVS 二极管,片外超低电容 TVS 用于高速接口。

- T-coil 网络:高速 I/O 专用,平衡 ESD 防护与信号完整性(带宽可达 10GHz+)。

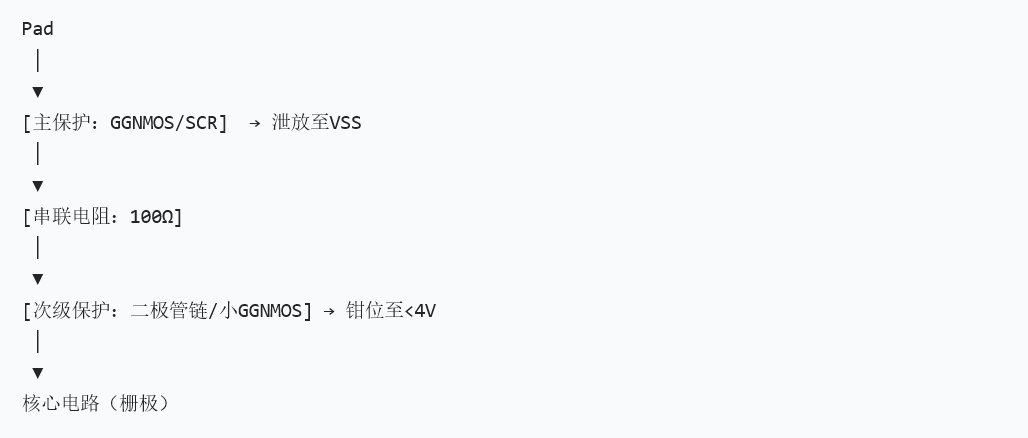

三、分级防护网络架构(最有效设计范式)

1. 两级 / 三级防护架构(I/O 端口)

(1)主保护(Primary)——Pad 附近,泄放主力

- 器件:GGNMOS、SCR、双向二极管。

- 功能:承受大部分 ESD 能量,快速将高压下拉至 10–15V 级。

- 要求:紧贴 Pad、低阻抗路径、Ballast 电阻、多 Finger 布局。

(2)次级保护(Secondary)—— 核心电路前,精细钳位

- 器件:小尺寸二极管链、低压 GGNMOS、RC 钳位。

- 功能:将残留电压进一步钳位至 **<4V**(安全窗口),保护栅极。

- 要求:靠近核心电路、串联小电阻(50–200Ω)限流、低寄生。

(3)缓冲电阻(ESD Resistor)—— 串联在主 / 次级之间

- 阻值:50–200Ω(多晶硅 / 扩散)。

-

作用:

- 限流,降低主保护器件电流应力。

- 分压,降低核心电路端电压。

- 隔离,减少 ESD 对信号的干扰。

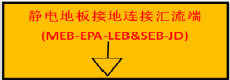

2. 电源域防护(Power Rail)

- 全局 RC-CLAMP:每对 VDD–VSS 至少 1 个,覆盖全芯片。

- 局部电源钳位:每个 IP 核 / 电源域独立钳位,抑制域间耦合。

- 电源–I/O 协同:I/O 保护器件泄放路径最终接入电源钳位网络,形成闭环。

3. 典型 I/O 防护拓扑(1.8V)

Pad → [主保护GGNMOS] → [串联电阻100Ω] → [次级二极管链(2×0.7V)] → 核心电路输入栅极

↓(泄放至VSS)

[全局RC-CLAMP]

四、版图设计关键技术(决定 ESD 成败)

1. 布局原则

- 防护器件紧贴 Pad:距离 < 50μm,减少走线寄生电感 / 电阻。

- 电源 / 地线短而宽:VDD/VSS 线宽≥50μm(HBM 4kV),采用网格 / 环状布线。

- 敏感区域隔离:核心电路与 ESD 器件保持≥25μm Keep-out 区,加双保护环(Guard Ring)抑制 Latch-up。

- 多 Finger 均匀布局:GGNMOS/SCR 采用叉指结构,Ballast 电阻均匀分布,避免电流集中。

2. 布线规则

- ESD 泄放路径优先:Pad→保护器件→地 / 电源的路径最短、最宽、无过孔。

- 避免单点接地:ESD 地与信号地分离,采用多点接地,防止地弹传导至核心电路。

- 金属层数:顶层金属(厚金属)用于 ESD 大电流路径,降低电阻。

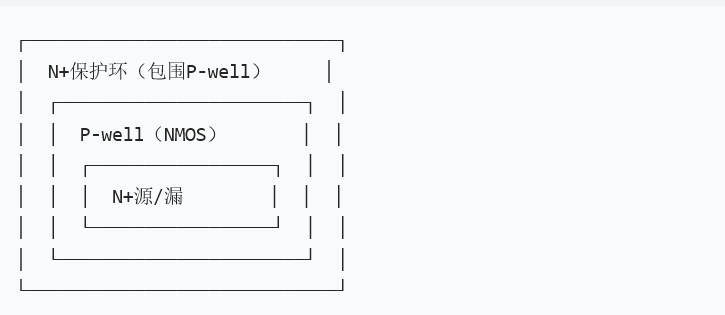

3. 闩锁抑制(Latch-up Prevention)

- 采用深 N 阱(DNW)、** 双阱(Twin-Well)** 工艺。

- 保护环(Guard Ring):N + 环包围 P-well,P + 环包围 N-well,间隔 < 10μm。

- 避免 I/O 与电源域直接相邻,增加隔离槽。

五、ESD 验证与测试(设计闭环)

1. 核心测试模型(JEDEC)

- HBM(人体模型):100pF 电容 + 1.5kΩ 电阻,模拟人体放电,最常用。

- MM(机器模型):200pF 电容 + 0Ω 电阻,模拟机器放电,更严苛。

- CDM(器件充电模型):芯片自身充电后放电,高速接口重点关注。

2. 设计验证方法

- TLP(传输线脉冲)测试:测量 ESD 器件 I–V 曲线,确定触发电压、钳位电压、二次击穿电流(It2)。

- HSPICE/SPICE 仿真:建模 ESD 器件,仿真脉冲响应、电压钳位效果。

- Latch-up 测试:验证电源–地短路风险,确保 ESD 触发后可恢复。

- 量产抽样测试:每批晶圆抽样 HBM/CDM 测试,确保良率。

六、高速 / 高压 / 先进工艺挑战与方案

1. 高速接口(USB4/PCIe 5.0/10G+)

- 挑战:ESD 寄生电容(>1pF)导致信号衰减、眼图闭合。

-

方案:

- 采用超低电容 TVS(Cj<0.5pF)。

- T-coil 网络:平衡阻抗与带宽,回波损耗≥20dB@10GHz。

- 串联匹配电阻(22–50Ω),优化信号完整性。

2. 高压工艺(5V/12V/40V)

- 挑战:ESD 触发电压需匹配高压工作窗口,避免误触发。

-

方案:

- 厚氧器件(FOD)+SCR 组合。

- 多级二极管链(如 5×0.7V)提升触发电压。

- 独立高压 ESD 域,与低压域隔离。

3. 先进工艺(FinFET/3nm/2nm)

- 挑战:栅氧更薄(<1nm)、漏结更浅、Latch-up 风险更高、ESD 窗口更窄。

-

方案:

- FinFET 专用 ESD 结构:基于 Fin 的 GGNMOS/SCR,提升均匀性。

- 3D 集成防护:TSV(硅通孔)集成 ESD 器件,缩短路径。

- 工艺协同优化:增加 Silicide Block、优化阱掺杂、提升 Ballast 电阻稳定性。

七、设计趋势总结

- 架构升级:从单一器件→多级协同 + 全域防护,覆盖 I/O + 电源 + 核心。

- 器件创新:SCR/LVTSCR/ 触发型结构成为主流,追求低钳位、高通流、小面积。

- 协同设计:ESD 与信号完整性、电源完整性、可靠性联合仿真。

- 工艺适配:先进工艺专用 ESD 结构与版图规则成为标配。

- 系统级集成:片上 ESD + 片外 TVS+PCB 防护,形成全链路防护。